Design of a Configurable, Massive-Parallel Vector Processor Architecture for Computer Vision and a Framework for the Implementation of Object Recognition Applications for Embedded Systems

| Led by: | apl. Prof. Dr.-Ing. G. Payá Vayá |

| Team: | Dipl.-Ing. S. Nolting, Dipl.-Ing. L. Gerlach |

| Year: | 2016 |

| Duration: | Mai 2016 - Oktober 2017 |

| Is Finished: | yes |

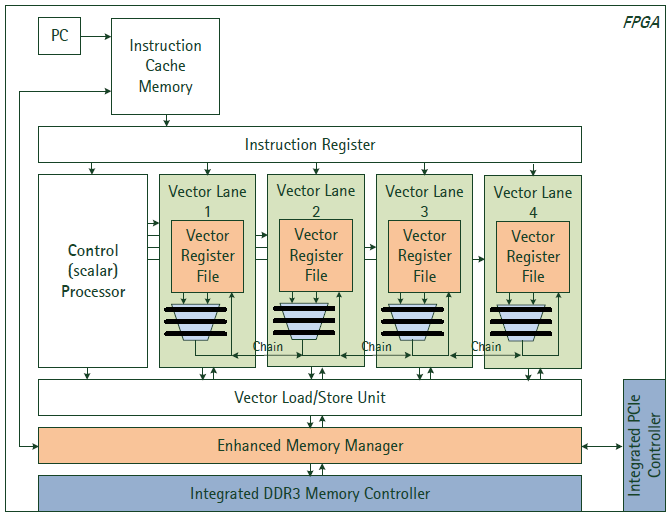

The increasing complexity of current computer vision algorithms for autonomous driving, such as object detection and classification using neural networks, represents a challenge for automotive system designers. Providing a real-time processing system under hard real-time constraints and a low energy (budget a few watts) is difficult to achieve even with current technical platforms. The goal of this project is to design a new approach of application-specific vector processor for FPGA implementation. The well-known overhead of other platforms (e.g. GPUs) shall be avoided by using several strategies: Novel functional mechanisms, a modular and customizable architecture and a suitable development framework, which is especially designed for the implementation of automotive applications.). An FPGA-based prototype will demonstrate the performance of the vector processor concept for a selected application at the end of the project.