Portierung, Kopplung und Optimierung einer generischen Vektorprozessorarchitektur auf ein Xilinx UltraScale+ MPSoC mit eingebettetem ARM Prozessor

| Betreuung: | Nolting, Stephan; Payá Vayá, Guillermo |

| Jahr: | 2018 |

| Laufzeit: | 01.02.2018- |

| Ist abgeschlossen: | ja |

Im Automobilbereich und im Kontext der Fahrerassistenzsysteme werden Architekturen für komplexe Berechnungen eingesetzt. Diese unterliegen harten Echtzeitanforderungen und müssen mit geringen Energiebudgets arbeiten können. Zur Situationsnalyse des Fahrzeuges sind unter anderem Information über andere Verkehrsteilnehmer erforderlich. Die massive Anzahl an erforderlichen Operationen zur Analyse der Situation stellt hohe Anforderungen an die eingesetzte Rechnerarchitektur. Neben niedriger Latenz spielt hierbei aber auch eine geringe Verlustleistung eine wichtige Rolle. Standardarchitekturen wie general purpose CPUs oder GPUs bieten hier keine optimale Lösung, da sie entweder nicht die erforderlichen Rechenleistungen erbringen oder aber eine zu hohe Leistungsaufnahme haben. Eine speziell für diesen Bereich der massiv-parallelen Fahrerassistenzanwendungen entwickelte Prozessorarchitektur stellt der VPRO Vektorprozessor dar.

Der für FPGAs optimierte VPRO bietet die notwendige Rechenleistung bei minimalen Energieverbrauch und erlaubt nicht nur eine spätere Modifikation der Hardware sondern durch die Programmierbarkeit eine softwareseitige Flexibilität Anwendungen im Nachhinein zu modifizieren bzw. auszutauschen. Um eine möglichst hohe Abstraktion der Hardware für die Entwicklung der Anwendungen zu bieten bietet sich ein partitioniertes Konzept an: Hierbei werden die rechenintensiven Aufgaben basierend auf hochoptimierten Bibliotheken auf den VPRO ausgelagert. Der Aufruf dieser Funktionen von der eigentlichen Anwendung aus geschieht über einen dedizierten Prozessor im FPGA, auf dem mittels gängiger Toolchains komplexe Aufgaben bis hin zu standardisierten Betriebssystemen implementiert werden können.

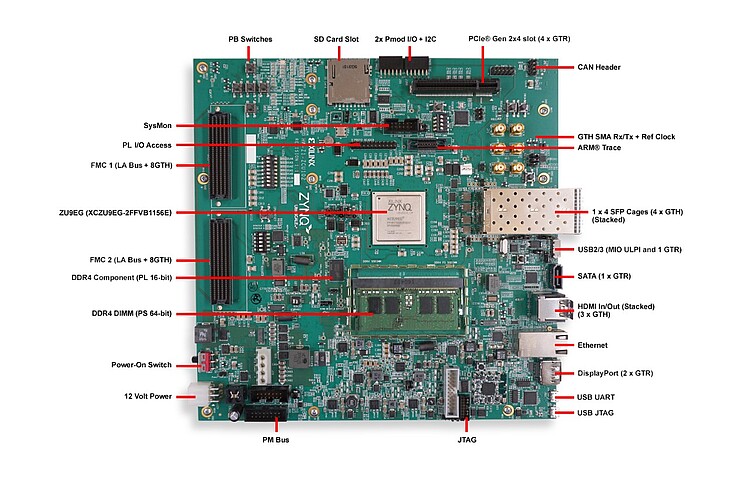

Im Rahmen dieser Arbeit soll die generische VPRO Vektorprozessorarchitektur auf das Xilinx UltraScale+ MPSoC portiert werden. Dabei soll auf Basis des AXI4 Standard eine Infrastruktur implementiert werden, welche unter anderem einen Speichercontroller sowie Kommunikationsschnittstellen enthält. Die Kopplung des Vektorprozessors mit dem im FPGA verfügbaren ARM Prozessor soll sowohl hardwareseitig über entsprechende Schnittstellen als auch softwareseitig über Treiber und Bibliotheken implementiert werden.

Für diese Arbeit sollten folgende Voraussetzungen erfüllt sein:

- Gute Kenntnisse in hardwarenaher C-Programmierung, sehr gute Kenntnisse in VHDL

- Allgemeine Kenntnisse von Prozessorarchitekturen und Konzepten der parallelen Verarbeitung

- Kenntnisse im Umgang mit Xilinx Vivado sind hilfreich aber nicht Voraussetzung

Die Arbeit kann in deutscher oder englischer Sprache verfasst werden.