3D-Floorplanning

| E-Mail: | markus.olbrich@ims.uni-hannover.de |

| Team: | M. Sc. Artur Quiring |

| Year: | 2014 |

| Duration: | completed |

| Is Finished: | yes |

Floorplanning is one step in physical design of integrated circuits (ICs). A set of modules (IP-Cores or a set of standard cells) has to be placed on a layer and the placement is driven by an optimization function, which is based on total chip area, wirelength and other optimization goals.

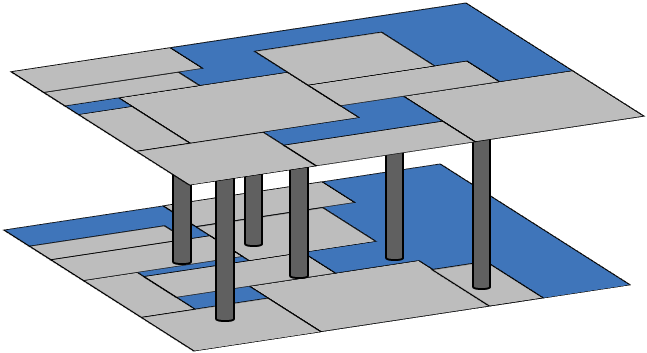

3D-Floorplanning extents the original problem, where it is now possible to place the modules above each other on different layers. This requires an adaption of the floorplanning algorithms and datastructures to enable the consideration of new optimization goals and constraints, like temperature and minimization of Throug-Silicon-Vias (TSVs).

Therefore, the main goal of this project is to develop new optimization algorithms and datastructures or to adapt already existent approaches, to cope with the 3D-Floorplanning problem. Furthermore, it should be investigated which design goals are relevant for 3D-Floorplanning and how they can be integrated into the optimization algorithms.