-

System and Circuit Concepts for High-Efficiency and High-Power Density 48V DC-DC ConvertersLed by: Niklas DenekeTeam:Year: 2023Duration: 15.6.2023-15.12.2023

-

Automatisierung der Analyse von analogen Schaltungen mit einer Arithmetik für ZufallsvariablenZur schnellen Analyse von statistisch verteilten Eigenschaften elektronischer Schaltungen wurde am Institut eine spezielle Arithmetik entwickelt. Die Eingabe analoger Schaltungen im Spice-Format und die Simulation dieser Schaltungen soll in dieser Arbeit automatisiert werden.Led by: Dr.-Ing. Markus OlbrichTeam:Year: 2021Duration: 1.12.2020-1.6.2021

![]()

![]()

-

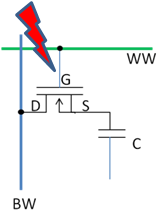

Design and Implementation of a Dead Time Control for ZVS and ZCS of a Multi-Level DC/DC ConverterMulti-Level-Schaltwandler bieten durch die zusätzlichen Spannungslevel bei hohen Übersetzungsverhältnissen Vorteile. Die zusätzlich benötigten Schalter erhöhen allerdings die Schaltverluste. Um dem entgegenzuwirken soll in dieser Arbeit eine totzeitbasierte Zero-Voltage-Switching-Regelung für Multi-Level-Wandler entworfen werden.Led by: Ferdinand PieperTeam:Year: 2021Duration: 1.12.2020-1.6.2021

-

Implementierung und Evaluierung eines beschleunigten Backprojection-Verfahrens zur SAR-BilddatengenerierungBeim „Synthetic Aperture Radar“ (SAR) können hochauflösende Luftbilder unabhängig von Tageszeit und Witterung generiert werden. Um die Verarbeitung der Sensordaten schritthaltend mit der Datenaufnahme (Echtzeit) zu gewährleisten, werden spezialisierte Hardware-Architekturen eingesetzt. Entgegen reiner Software-Implementierungen auf General-Purpose-Prozessoren müssen für diese Spezialhardware angepasste und optimierte Verfahren entwickelt werden.Led by: Cholewa, FabianYear: 2016

![]()

![]()

-

Implementierung und Evaluation einer Fuÿgängererkennung auf einem heterogenen RISC-FPGA-SoC mittels High-Level SyntheseLed by: Nicolai Behmann, M.Sc.Year: 2016

-

Simulation und Bestimmung des Einflusses von Strahlung auf das Verhalten von CMOS-Bausteine hinsichtlich ihrer StrahlungshärteDie Zuverlässigkeit von moderner Elektronik muss bestimmte Anforderungen erfüllen, damit die dauerhafte Funktionalität trotz Umwelteinflüssen gewährleistest werden. Diese elektronischen Bauteile werden heutzutage in vielerlei Bereiche verwendet wie z. B in der Medizintechnik, in der Luft- und Raumtechnik und in der Forschung. In diesen Anwendungsbereichen werden elektronische Komponenten in einer besonderen Umgebung betrieben, in der besonders hohe Strahlung herrscht.

![]()

![]()

-

Implementierung und Optimierung eines Vektor-Koprozessors zur Bildverarbeitung auf FPGAsDie steigende Komplexität von aktuellen Fahrerassistenz-Algorithmen, wie z.B. Objekterkennung und Klassifizierung mit neuronalen Netzen, stellt eine Herausforderung für die Automobilzulieferer dar. Das Bereitstellen einer schritthaltenden Verarbeitung (Echtzeitfähigkeit) ist selbst mit aktuellen Plattformen unter den gesetzten Rahmenbedingungen von wenigen Watt schwer zu erreichen. Das IMS beschäftigt sich mit der Erforschung eines neuen Ansatzes von applikationsspezifischem Vektorprozessor für FPGAs, der durch eine modulare Struktur und Konfigurierbarkeit leicht auf unterschiedliche Anwendungen angepasst werden kann.Led by: Hartig, Julian

![]()

![]()

-

Integration eines DSPs in eine Emulationsumgebung zur Untersuchung von Fehlerschutz-MechanismenAm Fachgebiet "Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme (IMS) werden in verschiedenen Projekten fehlertolerante Hardware-Architekturen erforscht. Unter anderem wird hierbei das Verhalten eines DSPs bei durch Strahlung verursachten Fehlern untersucht. Um kostspielige Experimente zu vermeiden, sollen derartige Untersuchungen auch emuliert werden. Hierzu verfügt das IMS über ein Matlabgesteuertes Framework mit dem es möglich ist, entsprechend eines vorgegebenen Fehlermodells, Fehler in eine Hardware-Architektur zu injizieren. Der DSP soll daher in dieses Framework integriert und ein Referenz-Algorithmus in Assembler auf dem DSP implementieren werden. Anschließend sollen die Eigenschaften des DPSs und des Algorithmus bei der Injektion mit einem bestimmten Fehlermodell untersucht werden. Des Weiteren sollen verschiedene Maßnahmen zum Schutz des DSPs entwickelt, implementiert und untersucht werden.

![]()

![]()

-

Implementierung von interaktiven Applets zur automatisierten Erzeugung von 3D-Modellen für druckbare mechanische LogikgatterDas Fachgebiet "Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme (IMS) lehrt in verschiedenen Veranstaltungen Grundlagen von Logik-Schaltungen. Zum besseren Verständnis von boolescher Algebra kann es hierbei hilfreich sein bestimmte Zusammenhänge durch mechanische Logikgatter zu verdeutlichen. Am Institut wurden hierzu neuartige, 3D-druckbare und konfigurierbare mechanische Logikgatter entwickelt. Diese können jede beliebige boolesche Funktion abbilden. Zur Konfiguration eines mechanischen Logikgatters ist eine Umformung und Minimierung der booleschen Ausdrücke erforderlich. Die 3D-Modelle zum Drucken der mechanischen Logikgatter stehen als kostenlose Downloads auf der Webseite des IMS für jeden zur Verfügung. Um die Funktionsweise und Konfiguration der Gatter für jeden leicht verständlich zu machen, soll die Webseite um interaktive Applets ergänzt werden. Diese sollen zum einen die logische Minimierung anhand verschiedener Verfahren verständlich darstellen. Zum anderen sollen automatisiert entsprechende mechanische Logikgatter visualisiert werden.

![]()

![]()

-

Untersuchung und Evaluation der Abbildunsgvarianten eines massiv parallelen Vektorprozessors auf die Intel Arria 10 FPGA-ArchitekturDie Aufgabe in dieser Arbeit ist es, den am Institut entwickelte und für Xilinx FPGAs optimierten VPRO Vektorprozessor auf die Intel Arria 10 FPGA Architektur zu portieren. Um eine möglichst hohe Rechenleistung zu erzielen, sollen die Rechenkerne des Vektorprozessors für die FPGA-Architektur optimiert werden.Led by: Nolting, StephanTeam:

![]()

![]()

-

Implementierung eines automatischen Tools zur effizienten Abbildung von CNNs auf eine VektorprozessorarchitekturDie Aufgabe dieser Arbeit besteht darin, ein CNN-Mapping-Tool zu implementieren, das eine allgemeine CNN-Beschreibung (z. B. für Tensorflow) als Eingabe verwendet und den entsprechenden C-Code für den VPRO-Prozessor erzeugt.Led by: Payá Vayá, Guillermo; Nolting, StephanTeam:

![]()

![]()