Christoph Riggers, M. Sc.

Christoph Riggers, M. Sc.

Telefon

Adresse

Schneiderberg 32

30167 Hannover

30167 Hannover

Gebäude

Raum

Christoph Riggers, M. Sc.

Telefon

-

Publikationsliste

Zeige Ergebnisse 1 - 4 von 4

Mobile SARS‑CoV‑2 screening facilities for rapid deployment and university‐based diagnostic laboratory. / Stanislawski, Nils; Lange, Ferdinand; Fahnemann, Christian et al.Mehr...

in: Engineering in life sciences, Jahrgang 23, Nr. 2, 2200026, 02.02.2023.Publikation: Beitrag in Fachzeitschrift › Artikel › Forschung › Peer-Review

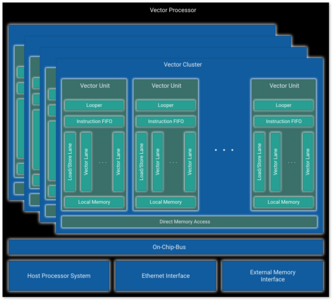

ZuSE KI-AVF: Application-Specific AI Processor for Intelligent Sensor Signal Processing in Autonomous Driving. / Thieu, Gia Bao; Gesper, Sven; Payá-Vayá, Guillermo et al.Mehr...

2023 Design, Automation and Test in Europe Conference and Exhibition, DATE 2023 - Proceedings. IEEE, 2023. (Design, automation and test in Europe conference).Publikation: Beitrag in Buch/Bericht/Sammelwerk/Konferenzband › Aufsatz in Konferenzband › Forschung › Peer-Review

Multicore performance prediction with MPET: Using scalability characteristics for statistical cross-architecture prediction. / Arndt, Oliver Jakob; Lüders, Matthias; Riggers, Christoph et al.Mehr...

in: Journal of Signal Processing Systems, Jahrgang 92, Nr. 9, 09.2020, S. 981-998.Publikation: Beitrag in Fachzeitschrift › Artikel › Forschung › Peer-Review

Parallelization strategies for fast factorized backprojection SAR on embedded multi-core architectures. / Wielage, M.; Cholewa, F.; Riggers, Christoph et al.Mehr...

2017 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS). IEEE Computer Society, 2017.Publikation: Beitrag in Buch/Bericht/Sammelwerk/Konferenzband › Aufsatz in Konferenzband › Forschung › Peer-Review

-

Forschungsprojekte

Prozessorarchitekturen

-

ZuSE-KI-AVF - Anwendungsspezifischer KI-Prozessor für die intelligente Sensorsignalverarbeitung im autonomen FahrenInnovative Fahrerassistenzsysteme erfordern neue, leistungsfähige Hardwareplattformen, die in der Lage sind, hochauflösende und mehrdimensionale Datenmengen in Echtzeit zu verarbeiten. Vielfältige Sensorik wie Kamera, Lidar oder Radar führt zu deutlich voneinander abweichenden Anforderungen, denen mit anwendungsspezifischer Hardware begegnet werden kann. Mit dem Ziel der Entwicklung einer solchen Hardware auf Basis einer skalierbaren und flexibel programmierbaren Architekturplattform hat das IMS erfolgreich an der ZuSE-Ausschreibung des BMBF zu Themen der künstlichen Intelligenz teilgenommen. In der Rolle der Projektleitung arbeitet das Institut in einem Konsortium an einer Open-Source Vektorprozessorarchitektur, die sich besonders für ressourcenintensive KI-Algorithmen eignet. Durch die vertikale Verarbeitung von Datenvektoren und komplexe Adressierungsmodi können neuronale Netze effizient berechnet werden. Für den Einsatz als Embedded-IP-Core in kommerziellen SoCs werden zudem Aspekte der funktionalen Sicherheit und IP-Security betrachtet. Auch die Entwicklung eines Compilers und eines effizienten Speichercontroller sind Teil des Projektes ZuSE-KI-AVF. Das IMS entwickelt an der Systemarchitektur, der Konzeption und Implementation von Algorithmen wie der Verarbeitung von Lidar-Punktwolken sowie einer Demonstration der Architektur auf Basis einer FPGA-Beschreibung.Leitung: Prof. Dr.-Ing. Holger BlumeTeam:Jahr: 2020Förderung: BMBFLaufzeit: Oktober 2020 - September 2023

![]()

![]()

-