OPARO

| Leitung: | Prof. Dr.-Ing. H. Blume |

| E-Mail: | 3621 |

| Team: | Dipl.-Wirtsch.-Ing. Sebastian Hesselbarth |

| Jahr: | 2014 |

| Ist abgeschlossen: | ja |

Während die FPGA-Emulation für die funktionale Optimierung und Verifikation inzwischen unerläßlich ist, können Verlustleistung und Temperaturverteilung von integrierten Schaltungen nur durch sehr aufwändige Simulationen bestimmt werden.

Aufgrund der hohen Rechenzeit für diese Simulationen besonders unter Beachtung realer Anwendungsszenarien lassen sich nur bedingt umfassende, iterative Optimierungen bezüglich Verlustleistung und Wärmeverteilung durchführen.

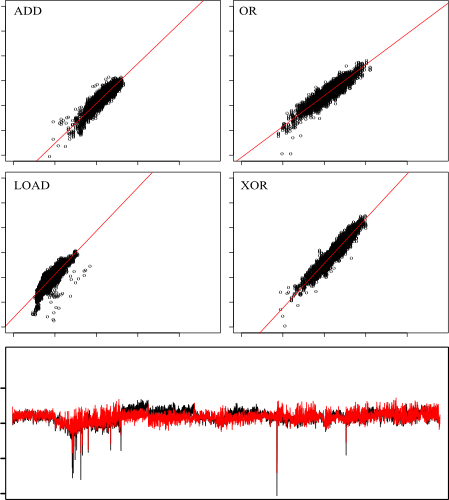

Ziel dieses Projektes ist es deshalb, präzise Modelle für die Bestimmung der Verlustleistung zu erarbeiten, die geeignet sind, auf FPGAs abgebildet zu werden und die während der funktionalen Emulation fortlaufend Verlustleistungswerte der eigentlichen Prozessoren zu generieren. Die Modelle sollen zudem im Vergleich zu den Verlustleistungsbestimmung durch Simulation eine hohe Genauigkeit bezüglich der Verlustleistungswerte und des zeitlichen Verlaufs der Verlustleistung aufweisen. Aufbauen auf der Emulation der Verlustleistungsmodelle soll untersucht werden, ob sich die FPGA-basierte Emulation auch für die Bestimmung von Temperaturverteilungskarten der Prozessoren anwenden lässt.