Bitte melden Sie sich über die zentrale Laboranmeldung UND im Stud.IP an!

Denken Sie unbedingt daran, die Vorkenntnisabfrage im Stud.IP (ILIAS) auszufüllen!

©

IMS-AS

©

IMS-AS

Inhalte

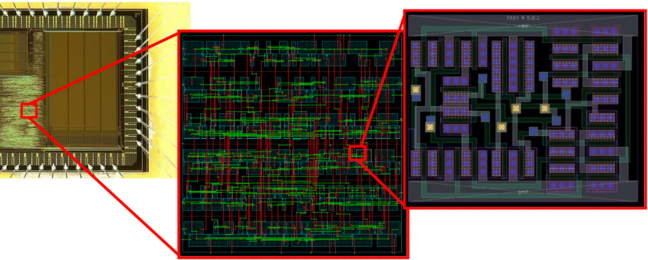

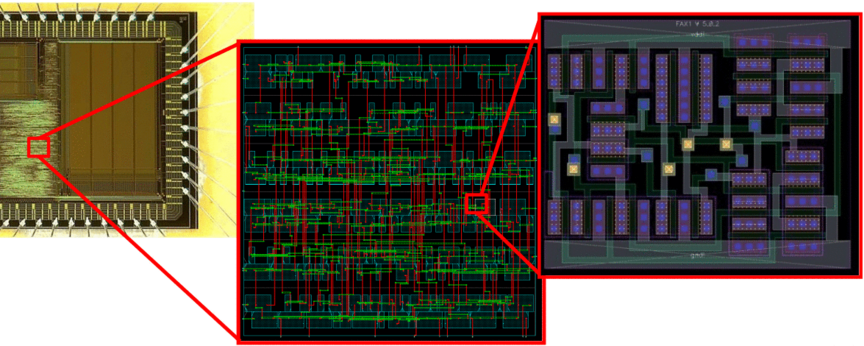

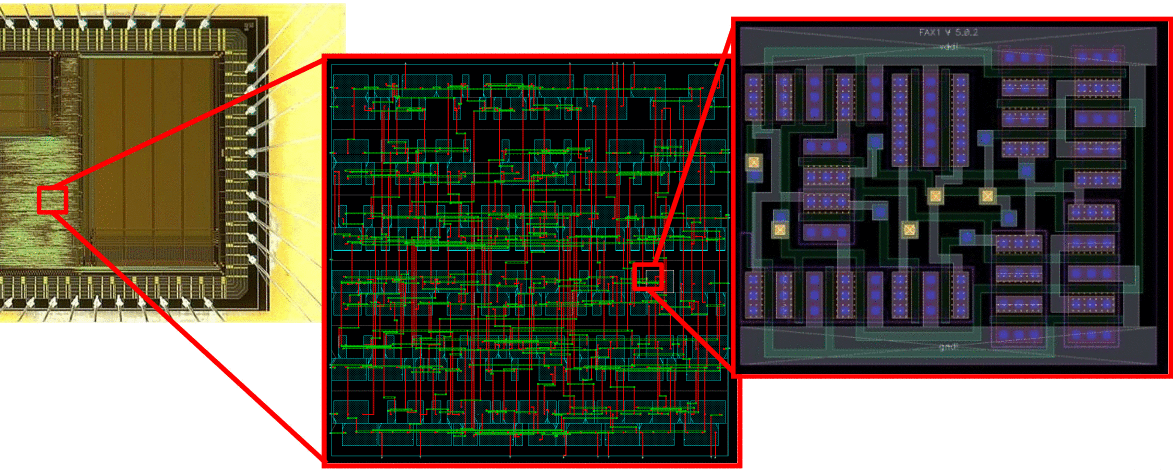

Die Studierenden erhalten im Rahmen dieser Veranstaltung einen Einblick in die unterschiedlichen Phasen des Entwurfs integrierter digitaler Schaltungen. Unter dem Einsatz industrieller Standardwerkzeuge sowie aktueller Open-Source Tools, wird in Teamarbeit ein Anwendungsspezifischer Mikrochip (ASIC) entwickelt.

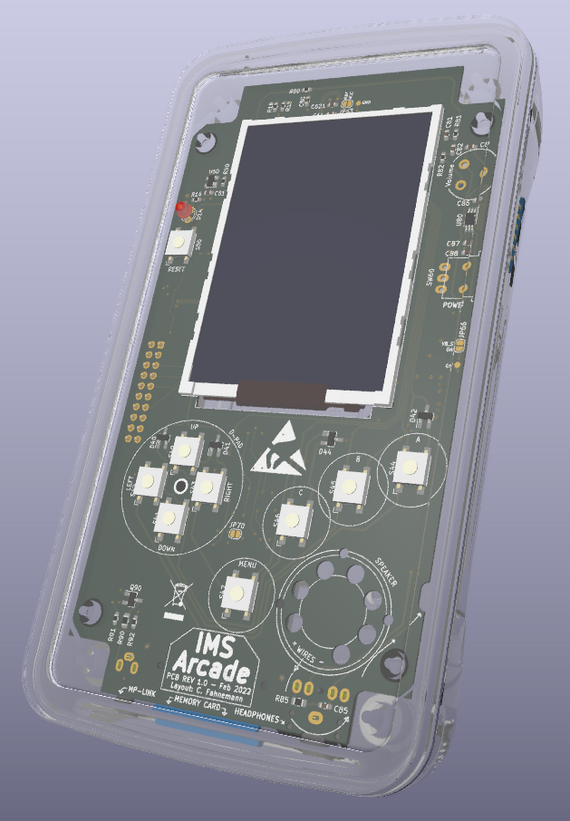

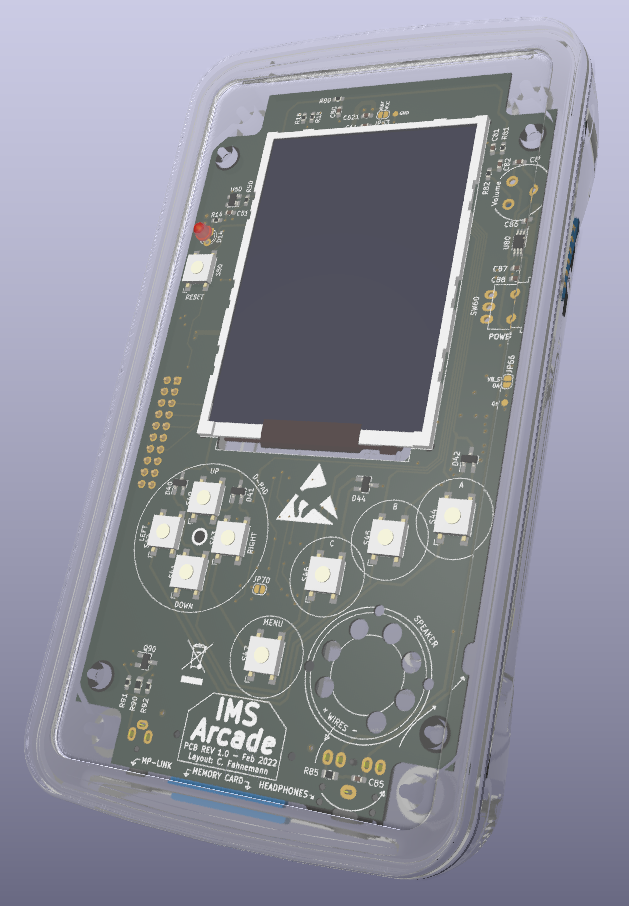

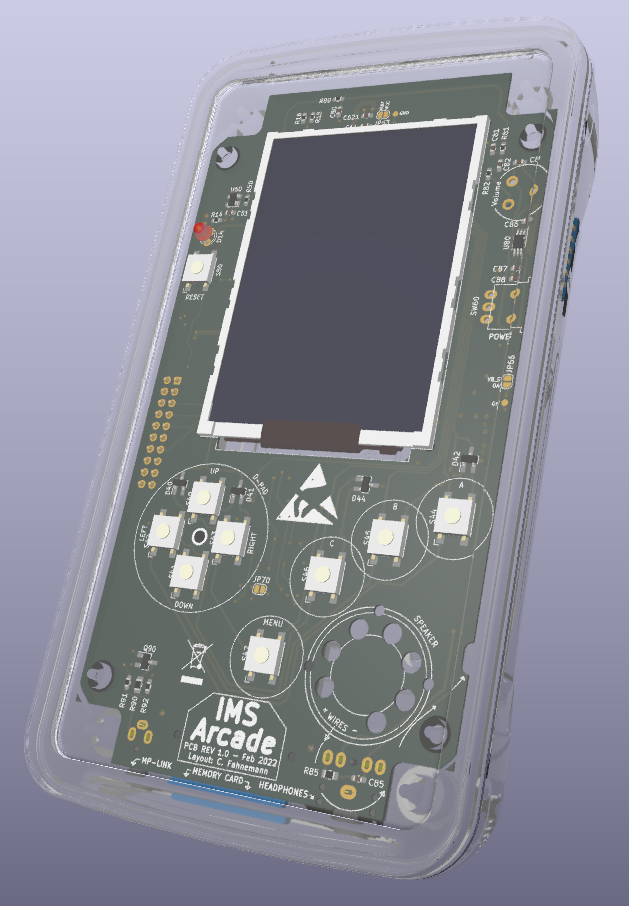

Anhand der praktischen Anwendung einer Handheld-Spielekonsole, die neben einem RISC-V-Hauptprozessor auch Hardwaremodule für z.B. Mehrspieler-Schnittstelle, Grafik- und Soundausgabe enthält, werden exemplarisch die Schritte der Chipentwickung durchlaufen. Hierbei wird ein Überblick über alle Aspekte gegeben, von der Spezifikation des Systems über die Implementierung eigener Hardware-Module bis hin zum physikalischen Layout. Zudem werden die Schnittstellen zwischen Hardware und Software (Firmware) sowie externen Bauteilen (Schaltungsdesign und Platinen-Layout) betrachtet.

Ein weiterer Fokus des Labors liegt auf der laufenden Verifkation: Die korrekte Funktion der Module wird sowohl durch Simulation am Computer als auch durch Emulation überprüft. Hierzu dient ein Hardware-Prototyp, welcher mit einem FPGA-Modul bestückt ist, das die Funktion der entwickelten Schaltung in Echtzeit abbilden kann.

Blockdiagramm des System-on-Chip

Ablauf und Termine

Jeweils Donnerstags ab 9:00 Uhr werden die nötigen Kenntnisse in einem interaktiven Seminarblock vermittelt. Anschließend wird bis ca. 14 Uhr* in selbstständiger Teamarbeit der jeweilige Entwicklungsschritt durchgeführt. Zu einigen Themen wird es Handreichungen geben, die zum jeweiligen Termin vorbereitet (gelesen) werden sollen.

Folgende Themenblöcke sind geplant:

- Projekteinführung: Planung, Spezifikation, System-on-Chip

- Schaltungsdesign: Schaltplan, Komponenten, Platinenlayout

- Embedded Software Programmierung, Memory Mapped I/O und Bit-Bang Emulation

- Hardware-Module in SystemVerilog erstellen und Simulieren

- Simulation mit dem Universal Verification Methodology (UVM)

- In-Circuit-Emulation auf dem FPGA

- ASIC-Synthese: Frontend und Backend

- Abschluss mit Vorträgen

*) Bei zügiger Bearbeitung ist es möglich, das Labor schon vor 14 Uhr zu verlassen. Es muss jedoch so geplant werden, dass eine Anwesenheit bis 14 Uhr möglich ist!

Teilnahmevoraussetzungen

Parallel zu der zentralen Laboranmeldung wird führen wir eine kurze digitale Vorkenntnisabfrage im Stud.IP durch. (Diese Abfrage wird auch als "Vortestat" bezeichnet, lassen Sie sich hierdurch aber bitte nicht abschrecken.) Bei Interesse an diesem Labor, melden Sie sich bitte im Stud.IP an!

Nötige Vorkenntnisse

Diese können aus verschiedenen Lehrveranstaltungen erworben werden. Es ist keine spezifische Veranstaltung verpflichtend.

- Grundlagen digitaler Systeme und integrierter Schaltungen

- Logikfunktionen, Gatter, CMOS, Transistoren

- Aufbau von einfachen Logik-/Arithmetikschaltungen

Empfohlene zusätzliche Vorkenntnisse

- Hardwarebeschreibungssprachen (z.B. Verilog, VHDL, Chisel - im Labor wird SystemVerilog eingesetzt)

- Programmiersprachen (z.B. C/C++, Python - im Labor wird C/C++ für Embedded-Schaltungen eingesetzt)

Anmeldung

Die Vergabe der Laborplätze erfolgt über die zentrale Laboranmeldung der Fakultät für Elektrotechnik und Informatik. Studierende aller Fakultäten müssen sich über dieses System für das Labor anmelden.

Aufgrund der begrenzten Teilnehmeranzahl ist zusätzlich das Ausfüllen eine Vorkenntnisabfrage ("Vortestat", siehe oben) erforderlich. Die Gruppeneinteilung erfolgt in der Einführungsveranstaltung. Darüber hinaus müssen Sie sich für diese Veranstaltung im Stud.IP anmelden.

Einführungsveranstaltung

Der erste Labortermin ist der 11.04.2024 um 9:00 Uhr. Eine Teilnahme an allen Seminarterminen sowie der Einführungs- und Abschlussveranstaltung ist verpflichtend.