Design and Implementierung einer generaischen FFT- und IFFT-Einheit zur Powerline-Kommunikation nach dem HomePlug 1.0.1 Standard

| Betreuung: | Stuckenberg, Tobias |

| Student/in: | Jannick Baumann |

| Jahr: | 2017 |

| Datum: | 23-11-17 |

| Laufzeit: | 23.05.2017-23.11.2017 |

| Ist abgeschlossen: | ja |

Am Fachgebiet „Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme werden

VLSI-Architekturen für Algorithmen der digitalen Signalverarbeitung mit besonderen Anforderungen

an Echtzeitfähigkeit und Verlustleistung konzipiert und implementiert. Ein Forschungsschwerpunkt

ist dabei die digitale Signalverarbeitung in der Kommunikationstechnik.

Heutige Anwendungen elektronischer Systeme setzen vermehrt auf die drahtlose Kommunikation

und den Austausch von immer größer werdenden Datenmengen untereinander. Am Institut für

Mikroelektronische Systeme werden unter anderem OFDM-basierte Kommunikationssysteme für

diese Anforderungen konzeptioniert und evaluiert. Ein besonders interessantes Verfahren ist hier die

Powerline Kommunikation. Diese ist ein Paket-basiertes Verfahren, welches nach dem Prinzip des

Ethernet-Stacks einen MAC- und einen PHY-Layer definiert.

Der PHY-Layer besteht im Wesentlichen aus einer Vorwärtsfehlerkorrektur für Daten und Header-

Informationen und einem OFDM-Modulationssystem. Letzteres moduliert die Frequenzinformationen

auf Subträger und ermöglicht so, im Falle von HomePlug 1.0.1, die Übertragung von Informationsbits

also Phaseninformation. Anschließend werden diese Informationen mit Hilfe einer Inversen Fast

Fourier Transformation (kurz: IFFT) in ein reelles Zeitsignal überführt. Diese IFFT-Einheit lässt sich

generisch in Hardware beschreiben und somit variabel in Flächenbedarf und Latenz ausführen.

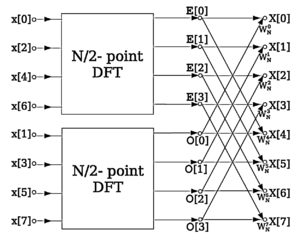

In dieser Arbeit soll eine generische IFFT- und FFT-Einheit in der

Hardwarebeschreibungssprache VHDL beschrieben und für ein Kintex-7 FPGA der Firma Xilinx

synthetisiert werden. Das Hauptaugenmerk bei dieser Aufgabe soll die Skalierbarkeit und der generische

Aufbau der einzelnen Butterfly-Stufen der Architektur sein. Diese sollen so effizient wie möglich

gestaltet werden, da sie den Hauptbestandteil der FFT- und IFFT-Einheit bilden. Am Ende der Arbeit

sollen vollständig evaluierte FFT- und IFFT-Einheiten in je einer seriellen und einer voll parallelen

Variante existieren. Optional soll die Reduzierung der Hardwaregröße durch Verwendung der

HomePlug 1.0.1 Frequenzmaske untersucht und verglichen werden.