Emulationsbasierte Simulation des Kommunikationsverhaltens eines parallelen Fahrerassistenzalgorithmus auf einem Manycore-NoC

| Betreuung: | Spindeldreier, Christian; Arndt, Jakob |

| Student/in: | Kevin Wohnrade |

| Jahr: | 2016 |

| Datum: | 28-11-16 |

| Laufzeit: | 12.05.2016-28.11.2016 |

| Ist abgeschlossen: | ja |

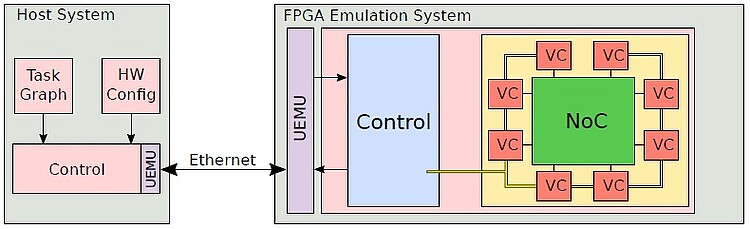

Am Fachgebiet „Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme werden unter anderen Architekturen der digitalen Signalverarbeitung, auch Multi- und Manycore-Prozessoren mit besonderem Fokus auf Echtzeitfähigkeit und Verlustleistung untersucht. Um während der Ausführung eines parallelen Algorithmus mit datenabhängigen Tasks, die Wartezeiten durch Kommunikationsoverhead möglichst gering zu halten, werden unterschiedliche Netzwerk-on-Chip (NoC) Topologien evaluiert. Da ein hoher Vernetzungsgrad der Recheneinheiten zwar eine schnelle Bearbeitung von parallelen Tasks, allerdings auch einen extremen Anstieg des benötigten Hardwareaufwands bedeutet, sollen reale Anwendungen möglichst genau simuliert werden können. Für die Analyse von NoC-Architekturen steht am Institut ein FPGA-basiertes Framework zur Verfügung, das die Abbildung von generischen Taskgraphen auf ein emuliertes NoC ermöglicht.

In vorangegangenen Arbeiten wurden bereits Laufzeitanalysen paralleler Fahrerassistenzalgorithmen auf verschiedenen Multicore- bzw. Manycore-Prozessoren durchgeführt. Ein am Institut entwickeltes Parallelisierungsframework ermöglicht dabei, Algorithmen auf diese Systeme effizient abzubilden und bietet darüber hinaus detaillierte Profilling-Möglichkeiten. Mithilfe der bisher gewonnenen Profiling-Daten soll nun eine detaillierte Nachbildung des Kommunikationsverhaltens einer realen Anwendung erstellt werden, um zunächst den emulationsbasierten Ansatz zur NoC-Analyse zu verifizieren.

Daher soll mithilfe der beiden beschriebenen Frameworks ein reales Profiling des „Histogram of oriented Gradients“ (HOG)-Algorithmus auf dem Intel Xeon Phi durch emulationsbasierte NoC-Simulation nachgebildet und zu evaluiert werden. Zunächst erfolgt die Einarbeitung in die bestehenden Frameworks und notwendigen Algorithmen, um anschließend ein geeignetes Profiling erstellen zu können. Anschließend soll das NoC-Framework so erweitert werden, dass die NoC-Architektur des Intel Xeon Phi Manycores nachgebildet werden kann. Dabei soll die Emulation des Xeon-Phi-NoC den realen Verlauf der Datenverarbeitung des HoG möglichst exakt abbilden, so dass weitere Anpassungen der Simulation notwendig werden können. Anschließend soll die NoC-Architektur variiert werden um die Eignung verschiedener NoC-Architekturen für den HoG-Algorithmus zu evaluieren.