Evaluierung approximierender arithmetischer Einheiten für Stochastic-Computing-Anwendungen in horizontalen und vertikalen SIMD-Vektorprozessoren

| Betreuung: | Weißbrich, Moritz |

| Student/in: | Kang Zheng |

| Ist abgeschlossen: | ja |

Schlagworte: VHDL, FPGA, ASIC-Design-Flow, Timing-Simulation und –Emulation, Verlustleistungsanalyse, Approximate Computing, Stochastic Computing

Eine effektive Möglichkeit zur Reduzierung der Leistungsaufnahme moderner Embedded-Computer-Vision-Systeme besteht in der Verringerung der Versorgungsspannung, wodurch jedoch eine Verlangsamung der internen Schalt- und Umladevorgänge und somit eine Verlängerung des kritischen Pfades berücksichtigt werden muss. Soll das Timing der Schaltung nicht verletzt werden, ist als Konsequenz eine geringere Taktfrequenz des verwendeten Prozessors zu wählen. Dies bedeutet einen unerwünschten Performanceverlust, der durch das Verfolgen neuartiger Ansätze ausgeglichen werden soll.

Stochastic-Computing-Ansätze gehen von der Annahme aus, dass der kritische Pfad nur von einer geringen Anzahl aller möglichen Berechnungen aktiviert wird, sodass bei Verletzung des Timings lediglich einige wenige Operationen des Prozessors fehlerhafte Ergebnisse liefern. Des Weiteren ist es eine Eigenschaft von Computer-Vision-Applikationen wie Merkmalsextraktion und Objekterkennung, dass z.B. aufgrund bereits verrauschter realer Eingangsdaten oder beschränkter menschlicher Wahrnehmung geringe Bildstörungen und somit stochastische Fehler tolerierbar sind. Dies eröffnet Potential, durch Übertakten gezielt das Timing zu verletzen und Performance-Gewinne zu erzielen, ohne dass die Funktionsfähigkeit der Algorithmen beeinträchtigt wird.

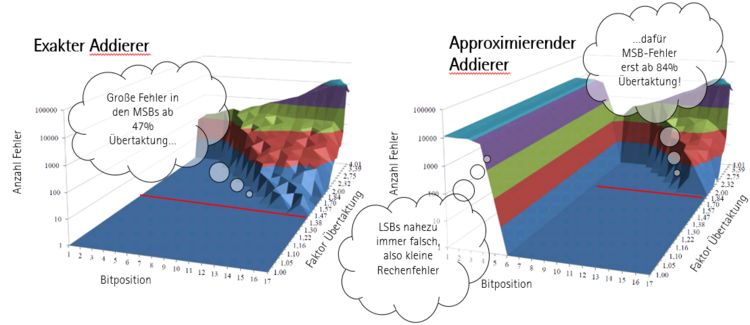

Weiterhin werden Approximate-Computing-Ansätze verfolgt, konventionelle exakt berechnende arithmetische Einheiten durch Blöcke zu ersetzen, die ein Näherungsergebnis ausgeben und günstigere Übertaktungseigenschaften zeigen können.

Der Abtausch zwischen stochastischer und approximativer Rechenungenauigkeit und Verlustleistung/Performance soll dabei im Rahmen dieser Arbeit anhand applikationsspezifischer horizontaler und vertikaler SIMD-Vektorprozessoren und einer Merkmalsextraktions-Applikation aus dem Computer-Vision-Bereich evaluiert und quantifiziert werden. Aufgabengebiete umfassen dabei unter anderem:

- VHDL-Implementierung approximierender Addierer und Multiplizierer für die o.g. Prozessorarchitekturen

- ASIC-Synthese des implementierten Designs

- Timing-Simulation und FPGA-basierte Emulation sowie Verlustleistungsanalyse zur Generierung quantitativer Daten bzgl. des Tradeoffs zwischen Rechenungenauigkeit, Performance und Verlustleistung