Implementierung und Optimierung einer Fehlerkorrekturanwendung auf Basis einer Transport-Triggered-Prozessorarchitektur

| Betreuung: | Weißbrich, Moritz; Gesper, Sven |

| Student/in: | Tuan Anh Dang |

| Jahr: | 2018 |

| Ist abgeschlossen: | ja |

Elektronische Steuerungssysteme für Untertage-Bohrungen zur Erdöl- und Erdgasförderung sind extremen Betriebsbedingungen ausgesetzt. Aufgrund vorherrschender Temperaturen von bis zu 250 °C ist der Einsatz von Hochtemperatur-Halbleitertechnologien erforderlich, welche eine gröbere Strukturgröße und ein langsameres Schaltungstiming als Standardtechnologien aufweisen. Dadurch sind Hochtemperaturschaltungen in ihrer Komplexität und Performanz beschränkt. Auch die Verlustleistungsaufnahme unterliegt aufgrund der beschränkten Kühlleistung bei hohen Temperaturen starken Limitierungen.

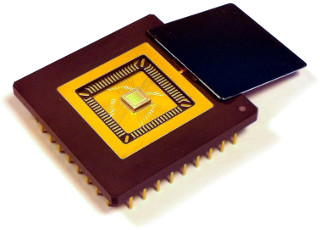

Trotz dieser technologischen Einschränkungen besteht ein moderner Bohrstrang aus vielzähligen Sensorik- und Steuerungsmodulen, zwischen denen eine flexible Kommunikation von Status- und Kontrollinformationen ermöglicht werden soll. Zur Datenübertragung steht dabei aufgrund der Umgebungsbedingungen lediglich das Energieversorgungsnetzwerk zur Verfügung. Für eine stabile Kommunikation macht dieser störungsbehaftete Kanal das Hinzufügen von Redundanz am Sender und eine Fehlerkorrektur am Empfänger notwendig. Damit Updates ohne kostenungünstige Anpassung der Hardware eingepflegt werden können, soll ein applikationsspezifischer Prozessor eingesetzt werden. Dieser muss zum einen die Designbeschränkungen für Komplexität und Verlustleistung einhalten, zum anderen aber auch durch spezialisierte funktionale Einheiten die notwendige Performanz zur Ausführung von Software-Fehlerkorrekturalgorithmen bereitstellen.

In dieser Bachelorarbeit soll eine Fehlerkorrekturanwendung auf Basis des Reed-Solomon-Codes in C implementiert und für eine Transport-Triggered-Prozessorarchitektur (TTA) optimiert werden. Mithilfe des TTA-Based Co-Design Environments (TCE) der Universität Tampere, Finnland, werden dabei die Spezialisierung der Architektur vorgenommen und umfangreiche Analyse- und Profilingmöglichkeiten für die Optimierung der Anwendung und des applikationsspezifischen Prozessors bereitgestellt. Auf Basis von ASIC-Synthesen sollen in einer abschließenden Evaluation die Eigenschaften des optimierten TTA-Prozessors bzgl. Chipfläche, Verlustleistung und Performanz mit Referenz-Architekturen in einer 350-nm-Hochtemperatur-Technologie verglichen werden.