Konzeptionierung und Implementierung einer parametrisierbaren Floating Point Unit für verschiedene FPGA-basierte Zielplattformen

| Betreuung: | Spindeldreier, Christian |

| Student/in: | Michael Rodin |

| Jahr: | 2015 |

| Datum: | 18-12-15 |

| Laufzeit: | 01.06.2015-18.12.2015 |

| Ist abgeschlossen: | ja |

Am Fachgebiet „Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme werden im Rahmen mehrerer Verbundprojekte VLSI-Architekturen für Algorithmen der digitalen Signalverarbeitung untersucht, wie z.B. im Projekt „Onboard SAR - Echtzeitdatenverarbeitung“. Das Prinzip des Synthetic Aperture Radar (SAR) ermöglicht die Generierung hochaufgelöster Luftbilder unabhängig von Tageszeit und Witterung. In diesem Projekt werden verschiedene Verfahren an spezifische Hardwarerestriktionen angepasst, um eine schritthaltende Prozessierung von SAR-Sensordaten zu ermöglichen.

Im Rahmen des Verbundprojektes QUANTUS – MAIUS werden für die Auswertung und Steuerung weltraumgestützter Experimente mit Bose-Einstein-Kondensaten (BEC) geeignete Hardwareplattformen und Realisierungen untersucht und evaluiert. Dabei liegt ein Fokus auf der Auswertung von BEC-Absorptionsbildern durch das Angleichen verschiedener Verteilungsfunktionen an die Bilddaten. In beiden Projekten wird für die Realisierung der Algorithmen bislang Festkommaarithmetik verwendet, was als wichtiger Schritt für eine effiziente und kostengünstige Hardwarerealisierung gilt, aber in der Regel mit einem relativ hohen Implementierungsaufwand verbunden ist.

Aktuelle Forschungsergebnisse zeigen jedoch, dass auch die Verwendung von Fließkommaarithmetik in einigen Bereichen durchaus geeignet ist, um effiziente Hardwarerealisierungen zu ermöglichen. So ist der Vergleich von in Fließkomma- und Festkommaarithmetik umgesetzten Algorithmenteilen für die Architekturoptimierung von entscheidender Bedeutung.

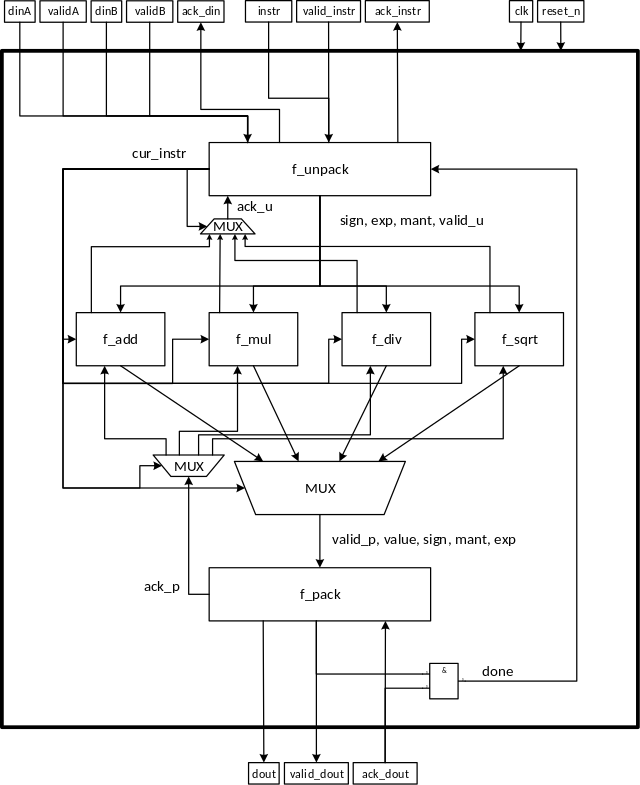

Daher soll eine parametrisierbare Floating Point Unit (FPU) konzeptioniert und in VHDL zu implementiert werden, welche die Grundrechenarten beherrscht. Zu diesem Zweck sollen verschiedene, allgemein bekannte Ansätze aus der Numerik unter Verwendung von Fließkommaarithmetik hinsichtlich ihrer Approximationsgüte und Effizienz untersucht werden. Die Implementierung und Analyse der gewählten Verfahren soll zunächst mit einer hardwarenahen Softwarelösung in Matlab umgesetzt werden. Um den Einfluss der Längen von Mantisse und Exponent zu untersuchen, soll die Floating Point Unit, zu dem generisch aufgebaut werden. Die implementierte FPU soll weiterhin kompatibel zu den in der IEEE 754-2008 Norm definierten Gleitkommadatentypen mit den Breiten 16, 32, 64 und 128 Bit sein. Weiterhin soll die VHDL-Beschreibung der FPU auf verschiedene FPGA-Plattformen abgebildet werden um den Ressourcenbedarf zu untersuchen.