Implementierung und Evaluierung eines CNN-basierten Szenenkennzeichnungsalgorithmus auf einer neuartigen komplexadressierenden Vektor-Co-Prozessor-Architektur

| Led by: | Nolting, Stephan |

| Is Finished: | yes |

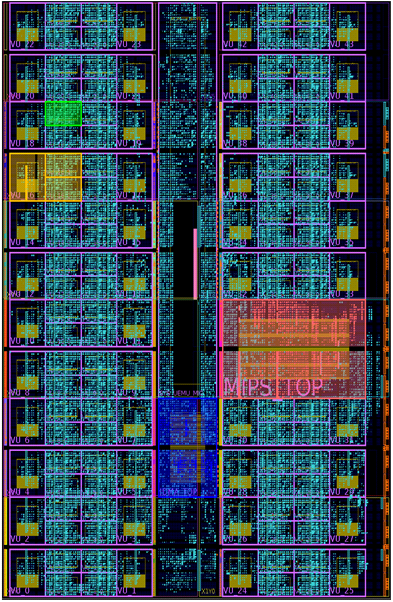

In der Forschungsgruppe "Architekturen und Systeme" des Instituts für Mikroelektronische Systeme werden Prozessorarchitekturen für hoch rechenintensive Aufgaben analysiert. Zum Beispiel sind komplexe Berechnungen unter harten Echtzeitbedingungen für den aufkommenden Bereich von Fahrerassistenzsystemen (Advanced Driver Assistance Systems, ADAS) erforderlich. Ein wichtiges Anwendungsfeld ist die intelligente Szenenanalyse. Convolutional Neuronal Networks (CNNs) sind eine vielversprechende Bild- und Videoerkennungstechnik hierfür. Um die enormen Rechenanforderungen zu erfüllen, stellen parallele Prozessorarchitekturen eine mögliche Lösung dar. Verschiedene kommerzielle Plattformen, wie GPU-basierte Ansätze oder CPUs mit parallelen Datenverarbeitungserweiterungen, existieren bereits. Aber gerade im Bereich der Embedded-Automotive-Anwendungen sind Energieeffizienz und Wirtschaftlichkeit ein besonders wichtiger Faktor. Daher ist die Implementierung einer parallelen Architektur eines anwendungsspezifischen Prozessors (ASP) erforderlich.

Die Aufgabe dieser Arbeit besteht darin, den Open-Source LLVM-Compiler derart zu modifizieren, dass er eine neuartige komplexe Vektor-Coprozessorarchitektur unterstützt. Die Funktionalitäten des Vektorprozessors soll durch Verwendung dedizierter C Intrinsics ermöglicht werden. Ein architekturunabhängiges Funktionsmodell der Intrinsics soll ebenfalls implementiert werden. Mit den Intrinsics soll dann eine CNN-Applikation zur Szenenanalyse auf die neuartige Vektorarchitektur abgebildet werde. Um die Leistungsfähigkeit des Systems zu erhöhen, sollen erweiterte Hardware-Modifikationen, wie Chaining und hierarchische lokale Speicherstrukturen, entworfen und ausgewertet werden.

Eine gute Dokumentation des Codes ist obligatorisch. Die eingereichten Kopien sowie die Ergebnisse der Arbeiten bleiben Eigentum des Instituts.